点击看:光刻机40年资本局:尼康起高楼,ASML宴宾客,美国楼塌了

芯榜

中国半导体排行榜。

课程开发背景

E课网在2016年上半年开发了面向集成电路(IC)设计行业的职业技能提升培训课程,主要针对即将毕业准备求职找工作的高年级本科生、研究生,和转型IC设计的职场人士。经过近四年的积累和发展,E课网建立和健全了数字IC设计、数字验证、DFT、数字后端设计、模拟IC设计、模拟版图设计和ATE测试等高端在线就业班,每年为行业提供大量的具有IC项目实战经验,熟悉主流IC设计方法、EDA设计工具和先进半导体工艺等集成电路高技能人才。

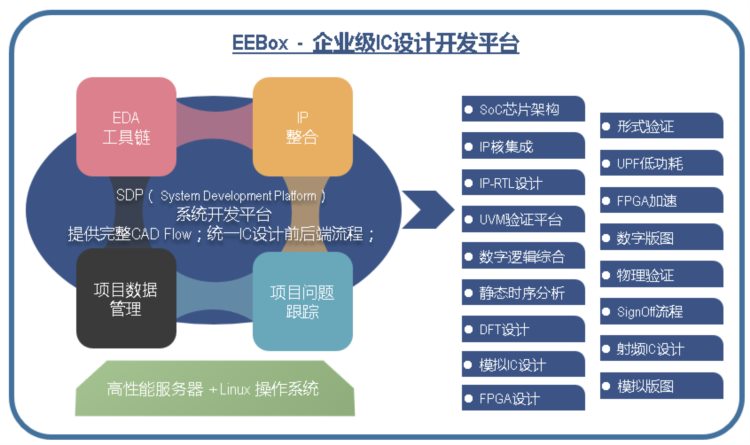

E课网集成电路设计方向的培训课程都是源于企业级的项目实践,从2018年开始,E课网历时2年,研发了EEBox – 企业级IC设计开发平台。基于该平台,E课网的IC设计实训班、就业班、技能提升班等课程贴近企业真实的IC设计项目,同时为企业、高校和研究院所提供高端的IC设计企业内训和定制化的项目案例。

EEBox– 企业级IC设计开发平台

EEBox是由摩尔精英E课网开发的一个IC设计开发平台,提供一个适用于开发大规模IC系统的完整解决方案,整合并优化了IC系统开发过程中需要的各个组件,包括:简化EDA工具使用、完善IP管理、管理项目数据库版本、跟踪项目开发进度和追溯项目问题等工程问题。

EEBox适用于ASIC、SoC、FPGA、AI、数模混合芯片、低功耗芯片、物联网芯片、通信芯片、音视频芯片等各类数字系统项目的开发和管理,可以大幅度提高IC设计工程师团队的开发效率、降低工程师团队之间的沟通成本、减少芯片开发过程的迭代次数、提升项目数据库的管理效率、降低EDA工具的使用难度、避免项目开发过程中低级人为错误。

DSDP(Digital System DevelopmentPlatform)是由shell、perl等脚本语言编写的一套IC设计开发工具,建立了完整的CAD Flow,支持统一的IC设计前后端流程。DSDP适用于Linux操作系统,方便移植,可以帮助ASIC/SoC/FPGA/AI/IoT等IC系统设计团队等快速构建完整的大规模IC系统开发平台,具备部署时间短、使用方便的特点。

EEBox可以完成复杂SoC芯片设计流程,支持主流的IC设计工具和工艺节点,涉及SoC芯片架构、IP核集成、RTL设计、代码风格检查、模块级和系统级功能逻辑仿真、UVM验证平台框架自动生成、 UVM寄存器模型RAL自动生成、仿真回归测试及RTL代码覆盖率自动收集、数字逻辑综合、静态时序分析、DFT设计实现、形式验证、UPF低功耗设计、数字自动布局布线、版图物理参数提取、数字版图物理验证以及芯片流片的SignOff流程。

E课网主打的6大IC设计就业班,主要是针对即将毕业求职的高年级本科和硕士应届生,以及想转型IC设计的职场人士,旨在帮助他们快速胜任岗位技能需求,成功就业。而对于大一到大三的低年级学生而言,可系统性学习的课程相对较少。

2019年开始国内各大高校都已陆续在本科阶段、甚至高职阶段开设微电子学院和集成电路设计专业,教育部批复建设28所示范性微电子学院,但大部分高校依然面临着IC设计专业师资匮乏的问题,所讲知识偏重理论,缺少IC设计的工程实践。

因此,以往有许多大一到大三的同学都向我们反映:我现在还不需要找工作,但是也想打好基础,为将来从事IC设计行业做好准备,是否可以在E课网从更简单的Verilog和数字IC电路开始系统性学习呢?

针对这一痛点,E课网特此面向所有理工科类在校大学生推出了IC成长E优计划——8周理论+上机实践的特训课程,从数字集成电路和Verilog硬件描述语言起步,然后到核心IC设计EDA工具和主流的CMOS工艺,通过项目实战来培养IC设计工程应用能力,帮助学生逐步成长为初级IC设计工程师,毕业挑战年薪30万!这些都是学校学不到的!

课程目标

精通Verilog语言

掌握常用的EDA工具使用

牢固掌握初级数字IC设计知识,成长为一名初级IC设计工程师

授课对象

所有想从事IC设计岗位的理工科类在校学生(大一到硕一均可)

授课内容

共96课时(48课时授课+48课时上机实训)

每课时为45分钟

序号 | 课程内容 | 课时 |

内容1: 基于HDL的设计流程 | 1.1 半导体集成电路发展趋势及IC产业链 1.2 超大规模数字集成电路设计流程 1.3 软硬件协同设计方法 1.4 基于标准单元库的ASIC设计流程 | 2 |

内容2: Verilog语言简介 | 2.1 硬件描述语言Verilog历史、应用和抽象层次 2.2 Verilog的基本语义和语法 -基本此法:注释、常量、字符串、标识符 -编译指令 -模块结构 -端口定义 -数据类型 -功能描述 | 2 |

Lab 1 (DONE) | 熟悉Linux操作系统和Gvim文本编辑工具 | 2 |

内容3: 数字逻辑仿真和testbench编程 | 3.1 数字逻辑仿真技术 -仿真算法 -数字逻辑仿真器 -波形数据 3.2 Verilog testbench -被测设计 -验证平台 -产生激励 -获取响应 3.3数字逻辑仿真工具的实践 -VCS的编译和仿真的指令 -VCS的图形化界面 -VCS的波形调试方法 -全加器的逻辑功能仿真 -自动化编译Makefile | 2 |

Lab 2: |

| 2 |

内容4: Verilog电路结构级描述 和 操作符 | Verilog的基本单元 层次化设计方法 Verilog的逻辑强度 Verilog的操作符 -算术操作符、按位操作符、逻辑操作符 -一元规约操作符、移位操作符、关系操作符 -相等操作符、相同操作符、条件操作符 -级联操作符、复制操作符 | 2 |

内容5: Verilog行为级建模 | Verilog行为建模的基本概念 Verilog中高级编程语言结构 -过程语句块 -时序控制语句 -阻塞赋值 -非阻塞赋值 连续赋值语句 过程复制语句 条件语句 循环语句 | 2 |

内容6: Verilog中的高级语法结构和可综合性编码风格 | Task任务的定义和调用 Function函数的定义和调用 有限状态机的建模方法 组合逻辑的可综合性描述 时序逻辑的可综合性描述 | 2 |

Lab 3 | IP设计实例 -FSM的设计方法:序列检测器 -饮料机 | 2 |

内容7: Verilog延时模型 | 块延时 分布延时 路径延时 时序检查 标准延时格式SDF | 2 |

内容8: Verilog库模型编译和文件操作 | IC生产厂商提供的Verilog库 Verilog文件加密 逻辑仿真器的相关问题 Verilog文本输出 读取仿真时间的系统函数 Verilog文件输入和输出功能 | 2 |

Lab 4 | IP的testbench编写和逻辑仿真 -同步FIFO -异步FIFO和格雷码 | 2 |

内容9: 数字逻辑综合 | 逻辑综合的基本概念 逻辑综合的基本流程 逻辑综合工具Design Compiler 逻辑综合约束 逻辑综合结果分析 脚本介绍 现场演示 | 2 |

内容10: 静态时许分析 | 静态时许分析的原理 静态时许分析的流程 同步电路的时序验证 建立时间 保持时间 静态时许分析报告 静态时许分析工具演示 | 2 |

Lab 5 | 数字逻辑综合 静态时序分析 | 2 |

内容11: 数字版图设计一 布局布线 | 数字版图设计的基本概念 数字版图设计的流程 数据的准备 版图布局 时钟树综合 版图布线 脚本介绍 现场演示 | 2 |

内容12: 数字版图设计二参数提取 | 时序延时信息提取 QRC -RC寄生参数提取 -RC参数文件SPEF介绍 -使用QRC软件对RC参数提取 -QRC的输入和输出 -QRC的提取流程 静态时序分析 Tempus -时序的基本概念 -如何分析时序路径 -Tempus的输入和输出 -静态时序分析的流程 | 2 |

Lab 6 | 数字版图设计实践 时序参数提取 | 2 |

内容13: 带时序信息的门级网表的后仿真 (动态时序逻辑仿真) | 时序信息提取 时序信息导入 动态仿真结果分析( vcs 实例演示) | 2 |

内容14: 形式验证和物理验证DRC与LVS | 形式验证 -基本概念 -一致性检查 -形式验证的流程 -形式验证工具的使用 物理验证 -物理验证工具 -DRC验证流程 -LVS验证流程 | 2 |

Lab 7 | 形式验证工具实践操作 DRC和LVC的物理验证工具实践操作 | 2 |

内容15: 可测试性技术DFT | 芯片测试的概念 DFT架构简介 边界扫描测试简介 JTAG 设计的可测性 缺陷模型 扫描链和ATPG的设计流程 扫描压缩 | 2 |

内容16: 存储器和内建自测试 | 存储器的类型 存储器的缺陷 内建自测试的算法:MarchC | 2 |

Lab8 | DFT Compiler的基本使用 | 2 |

课程实验和项目具体说明:

实验:包括实验手册和实验数据

随堂实验课程,每个实验,至少安排2个课时

Lab1:Linux操作系统基础

Lab2:逻辑仿真技术 – QuestaSim、VCS或IES

Lab3:Verilog RTL设计实例– checker/drink

Lab4:IP的设计与仿真 – fifo

Lab5:逻辑综合技术 – DesignCompiler + 静态时序分析 – PrimeTime

Lab6:布局布线技术 – IC Compiler

Lab7:形式验证和物理验证 – Formality & Calibre

Lab8:扫描链插入技术 –DFT Compiler

项目IP的设计流程

综合运用所学的ASIC设计方法,实现以下IP的设计,每个项目需要4到6小时。

1. ALU(adder/counter)的前端设计验证和后端设计

2. 序列检测器的前端设计验证和后端设计

3. 饮料销售机的功能设计验证后后端设计

4. 同步FIFO的前端设计验证和后端设计

5. 异步FIFO的前端设计验证和后端设计

6. RISC8的前端设计验证和后端设计

讲师介绍

孙博士 E课网课程负责人兼科学家

历任中电集团芯片设计专家,生物电子芯片行业应用方向团队负责人。参与过国家863项目,且曾主持一江苏省自主创新及成果转化专项,发明专利十余项,专业论文十余篇。对数字集成电路设计相关技术的原理,以及核心芯片设计EDA工具和主流芯片设计CMOS工艺都具有深入的研究。

学习方式

E课网教育平台在线学习(一年)

+

远程服务器登录实训(8周)

+

纸质讲义

+

终期考核

+

讲师互动答疑

+

班级群管理

开课时间

2020年4月20日(周一)晚上20:00开课

共96课时(理论+上机实践),为期8周~

授课安排:

在线学习:每周一 、周三、周五20:00PM ~ 22:00PM

在线实训:每周二 、周四、周六20:00PM ~ 22:00PM

在线答疑:周日 20:00PM ~ 22:00PM

IC高技能人才证书

完成课程后,可参加摩尔精英-E课网集成电路高技能能力认证考核,考核通过的同学可以获得摩尔精英-E课网颁发的集成电路高技能能力认证证书,为自己的数字IC设计能力提供有力证明。

(证书参考图)

课程费用

3999元

前20名学员可领取1000元课程优惠券

实付2999元

报名/咨询

或在浏览器中填写https://jinshuju.net/f/PwS1oN 咨询/报名

E课网(www.eecourse.com)是摩尔精英旗下专业的集成电路教育平台,致力于半导体行业高质量集成电路专业人才的培养。平台以集成电路企业岗位需求为导向,提供贴合企业环境的实训平台,通过线上线下的培训方式, 快速培养学员符合企业需求。

E课网拥有成熟的培训平台、完善的课程体系、强大的师资力量,规划中国半导体精品课程体系168门,涵盖整个集成电路产业链,并拥有4个线下实训基地。至今深度培养总人数15367人,为行业直接输送专业人才4476名。与143所高校建立深度合作关系,共举办企业专场IC培训240场。